東京--(BUSINESS WIRE)--(ビジネスワイヤ) -- 東芝は、業界最先端である0.13μm世代のアナログパワー半導体向けプロセスにおいて、トランジスタ構造の最適化により静電気放電特性を改善させ、当社の既存素子と比較して、静電気放電耐量を4倍向上させるとともに、放電耐量のばらつきを12分の1に低減しました。また3次元シミュレーションを用いた解析では、トランジスタ構造の改良による耐量向上のメカニズムを実証しました。当社は、本成果をチェコにて開催される半導体国際学会「ISPSD2016」にて、6月14日(現地時間)に発表しました。

半導体素子は、帯電した人体や機器からの静電気放電により、素子内に放電電流が流れ、局所的な発熱等により素子が破壊される可能性があることから、内部回路を保護する放電保護素子を配置して、半導体チップの静電気破壊を防止しています。特に使用電源電圧が10V~100Vと高く、高耐圧素子が必要となるアナログパワー半導体では、大電流を流すために静電気放電保護素子のサイズを大きくする必要があることから、チップの小型化を実現するための課題となっていました。

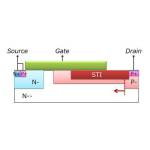

当社は、3次元シミュレーションにより、シリコン内で電界が集中する箇所を電流が流れ、格子温度が上昇することが熱破壊に至る主な要因であることを見出しました。この結果に基づき、トランジスタのドレイン側拡散層をソース側へ伸長することで、シリコン内の低抵抗領域は横方向に広がり、さらに、高電界箇所であるドレイン下を流れていた電流の経路を横方向に広げることで、高電界箇所と電流経路を離す構造となり、静電気放電耐量を4倍向上させ、放電耐量のばらつきを12分の1に低減させました。また、これにより静電気放電耐量の一つの指標である人体モデル±2kVを充たすチップ内の静電気放電保護素子の大きさを従来から32%に縮小しました。

当社の0.13μm世代のアナログパワー半導体プロセスでは、CMOS、DMOS、バイポーラなどのトランジスタおよび抵抗やキャパシタなどの受動素子を混載し、主に車載向けの「BiCD-0.13」(DMOSの耐圧~100V)、主にモーター制御向けの「CD-0.13BL」(DMOSの耐圧~60V)、主に電源向けの「CD-0.13」(DMOSの耐圧~40V)があり、用途に合わせたプロセスの選択が可能です。

当社は、2017年度に本技術を適用したCD-0.13プロセスのアナログパワー半導体を製品化する予定です。また、今回の成果をもとに、今後も他のアナログパワー半導体プロセスや素子の静電気放電耐量の向上を実現していきます。

Contacts

本資料に関するお問い合わせ先:

株式会社東芝 ストレージ&デバイスソリューション社 企画部 広報・IR担当

田中 耕一/山路

航太

Tel: 03-3457-3576

E-mail: semicon-NR-mailbox@ml.toshiba.co.jp